Basic Components

信号类型和常量¶

宽度:n.W

类型:<Type>(Width)

Bits(8.W) // Bit's vector

UInt(8.W) // Unsigned int

SInt(10.W) // Signed Int, 2' complement

Bits(n.W)

c.<T>[(Width)] 自动宽度推断

Bit extraction VS Width

1.U(32):1的第32位

1.U(32.W):32'b1

进制:"Str".<T>

'Char'.<T> ASCII 编码

逻辑值:[true|false].B

组合电路¶

逻辑操作:自动宽度推断

算数操作:自动宽度推断val add = a + b

val sub = a - b // max(|a|, |b|)

val neg = -a

val mul = a * b // |a| + |b|

val div = a / b

val mod = a % b // |a|

:= 用于值更新

位选:x(n[, m])

连接:Cat(a, b[, ...]) a ## b

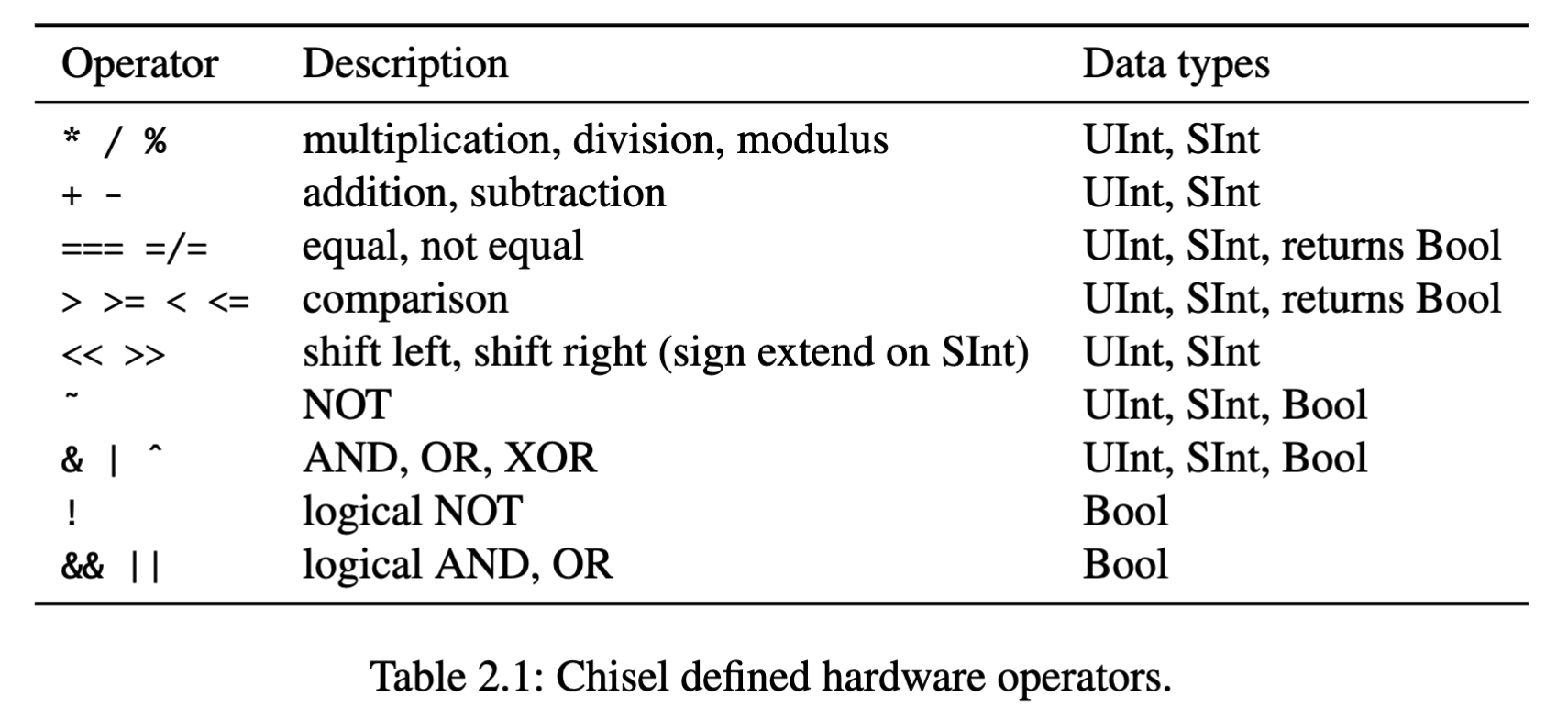

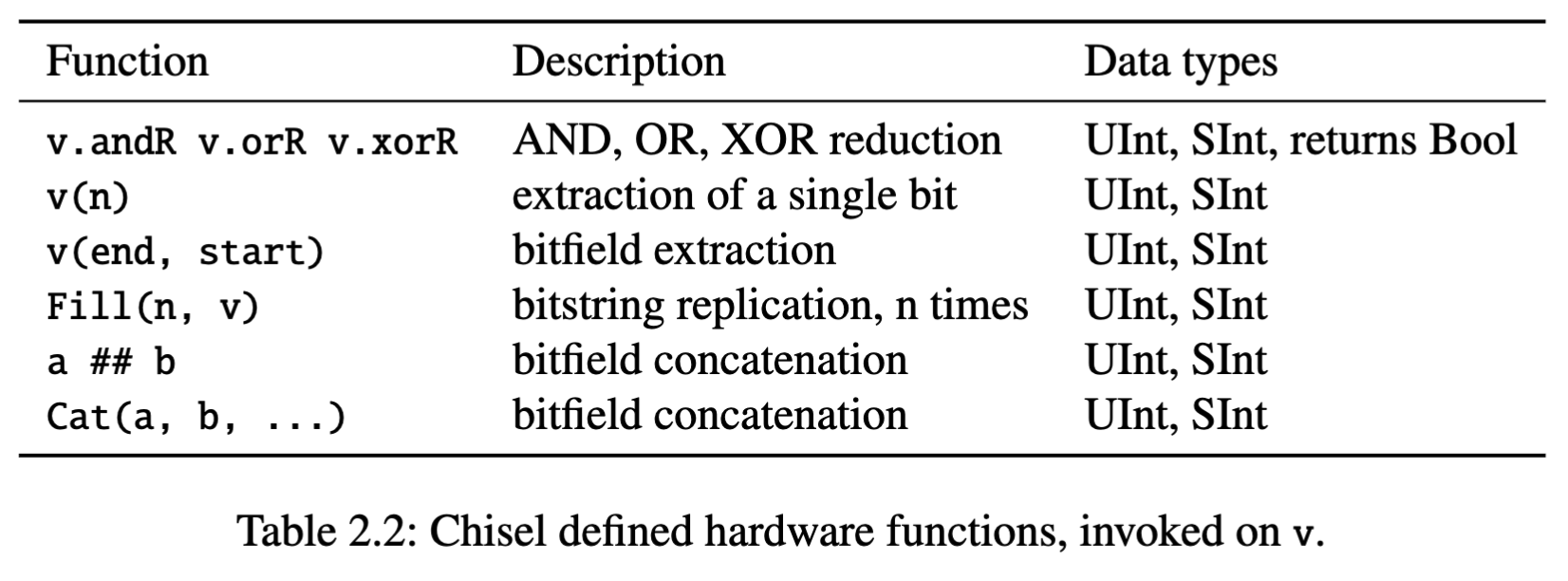

操作符:

操作函数:

操作函数:

Mux:

Mux:Mux(S, a, b)

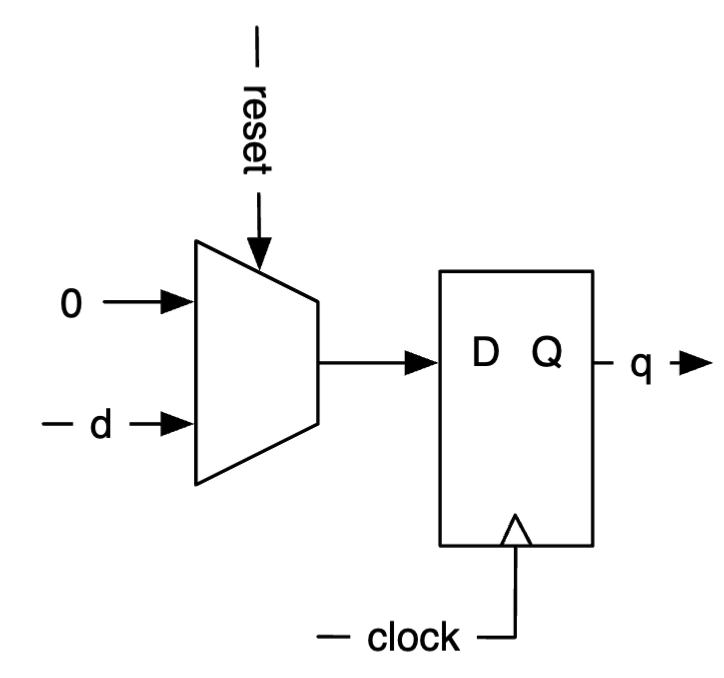

寄存器¶

编程模型

默认全局时钟 + 同步复位

定义:RegInit(c) RegInit(d[, c])

val reg = RegInit(0.U(8.W)) // 8-bit reg initialized with 0

val nextReg = RegNext(d) // connected to input at definition

val bothReg = RegNext(d, 0.U) // connected to input & initial value

结构¶

Bundle¶

Bundle:组合不同类型信号 + 子信号称作域(field)

定义:类继承

实例化:Wire(new C())

成员访问:

Vec¶

Vec:组合相同类型信号

- 通过下标访问

Vec VS Seq

Vec使用场景:

- 硬件动态寻址(Mux)

- 寄存器堆

- 模块端口

其余描述一系列事物应选择Seq

组合Vec¶

组合Vec:Mux

定义:Wire(Vec(n, Type)) VecInit([c|Sig][, ...])

val v = Wire(Vec(3, UInt(4.W)))

val defVec = VecInit(1.U(3.W), 2.U, 3.U)

val defVecSig = VecInit(d, e, f)

val vec = Wire(Vec(3, UInt(8.W)))

vec(0) := x

vec(1) := y

vec(2) := z

val muxOut = vec(sel)

when (cond) {

defVec(0) := 4.U

defVec(1) := 5.U

defVec(2) := 6.U

}

val vecOut = defVec(sel)

寄存器Vec¶

组合Vec:RegFile

定义:Reg(Vec(n, Type)) RegInit(VecInit([c|Sig][, ...])) 指定寄存器初始值

val regVec = Reg(Vec(3, UInt(8.W)))

val InitReg = RegInit(VecInit(0.U(3.W), 1.U, 2.U))

// use seq to do batch initialize

val resetRegFile = RegInit(VecInit(Seq.fill(32)(0.U(32.W))))

val dout = regVec(rdIdx)

regVec(wrIdx) := din

val resetReg = initReg(sel)

initReg(0) := d

initReg(1) := e

initReg(2) := f

RV32 寄存器堆

Bundle, Vec组合¶

Vec套Bundle:

Bundle套Vec: Bundle寄存器:先创建初始值的Wire,再转Regval initVal = Wire(new Channel())

initVal.data := 0.U

initVal.valid := false.B

val channelReg = RegInit(initVal)

部分赋值

对于

Chisel3中需使用Bundel实现 问题:需知道Bundle -> Bits 时的顺序 解决:使用Vec[Bool]Wire, Reg & IO¶

Chisel类型 VS 硬件:

UInt,SInt,Bits不代表硬件- 只有将Chisel类型用

Wire,Reg,IO包裹才生成硬件- Wire:组合逻辑

- Reg:寄存器(D 触发器的集合)

- IO:模块引脚

= VS :=:

- 创建硬件(命名):

val <name> = [Wire|Reg|IO](<Type>())- 使用常值变量(val)创建

- 带初始值硬件:

WireDefault,RegInit,VecInit- 尽管Chisel进行自动宽度推断,定义时最好指定宽度

- 已有硬件赋值:

:=- 条件赋值:每个条件均需赋值

- Chisel不允许锁存器

- 条件赋值:每个条件均需赋值

Chisel 是硬件语言

Chisel生成硬件,所有代码生成硬件,并行执行